自8月首批沟槽型MOSFET器件晶圆下线以来,九峰山实验室持续攻克碳化硅工艺技术难关。近日,实验室在碳化硅超结领域取得新进展:完成具有完全自主知识产权的碳化硅多级沟槽超结器件新结构设计,优化后的超结肖特基二极管可以实现2000V以上的耐压,比导通电阻低至0.997m?·c㎡,打破了碳化硅单极型器件的一维极限。同时该超结器件的多级沟槽刻蚀核心工艺研发也已完成。

九峰山实验室聚焦下一代功率器件技术的研究,形成了自主可控的成套工艺技术。本文是九峰山实验室功率器件研究组发表在《化合物半导体》杂志上的文章节选,围绕下一代SiC沟槽器件技术介绍业界相关研究进展与阶段性成果,并对九峰山实验室的研究成果展开详细介绍。

作者:袁俊 王宽 郭飞 徐少东 成志杰 陈伟 吴阳阳 彭若诗 朱厉阳 李明哲

团队介绍

袁俊

九峰山实验室碳化硅领域首席专家

带领团队专注于宽禁带半导体新型功率器件技术研究。从材料基础,器件工艺,器件结构和可靠性等共性技术问题出发,重点突破了下一代碳化硅沟槽器件技术、新型SiC沟槽MOSFET及成套工艺技术、新型氧化镓器件及制备技术等。这些核心器件技术的研究将为未来新能源汽车,高效率高功率密度的光伏风能等电力系统提供重要的技术支撑。

下一代碳化硅沟槽器件技术

功率半导体器件是电力电子装置中电能转换与电路控制的核心元器件,随着近年来新能源汽车、光伏、轨道交通、智能电网等产业的发展,市场对功率器件的需求迅速升温。第三代半导体SiC材料在禁带宽度、导热性能、临界击穿场强、电子饱和漂移速度上的优势明显,符合未来电力电子系统小型轻量化、高效一体化、安全可靠化的发展趋势。随着SiC功率器件的演进,沟槽结构成为二极管与MOSFET器件的主流设计。国外对于SiC沟槽器件的研究较早,二极管与MOSFET均已有产品上市,而国内对SiC平面器件的技术研究较多,在沟槽器件的研究上处于起步阶段。九峰山实验室聚焦于下一代SiC沟槽器件领域的研究,集中资源开发了SiC沟槽器件制备中的沟槽刻蚀、高温栅氧、离子注入等关键核心单点工艺,形成了自主可控的成套工艺技术。

碳化硅多级沟槽二极管技术

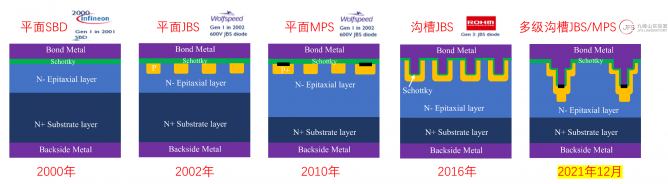

(图1 SiC二极管技术发展路线)

为了解决SBD反向漏电流较大的问题,ROHM在2016年发布了沟槽型JBS,通过刻蚀沟槽后再离子注入,得到了更深的P型掩蔽区,使得器件的反向漏电流进一步降低,但同时也在导通时带来了更加严重的JFET效应。

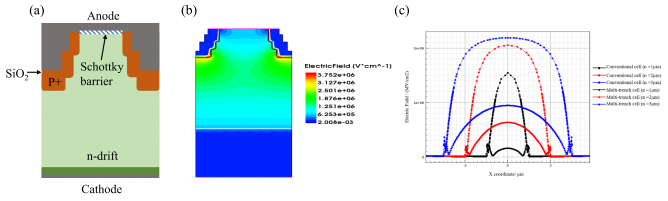

(图2 SiC多级沟槽JBS结构示意图及电场仿真:(a)多级沟槽JBS结构示意图;(b)多级沟槽JBS反向承压电场的TCAD仿真结果;(c)多级沟槽JBS与传统JBS表面电场分布的对比)

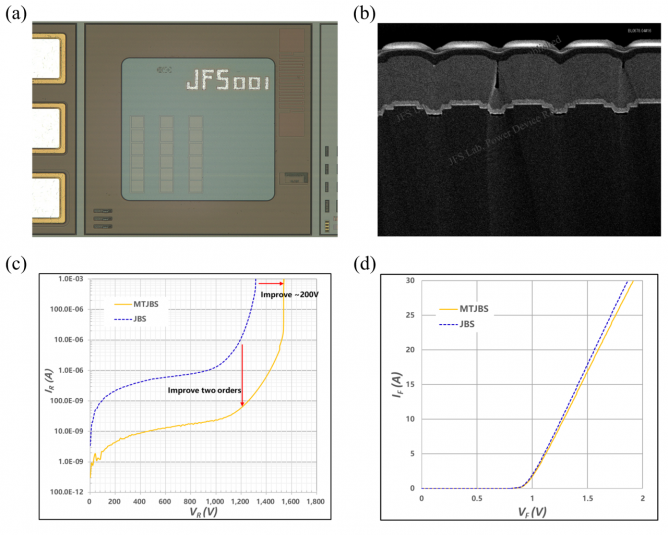

为了有效缓解SBD反向漏电流(深P掩蔽)与正向导通电阻(P区JFET电阻)之间的矛盾,九峰山实验室在2021年设计了SiC多级沟槽JBS/MPS[3]。如图2(a)所示,通过在金属/半导体接触界面设计多级台阶沟槽,可以使得P型离子沿沟槽方向注入更深,构造更好的电场屏蔽。为了实现上述设计,九峰山实验室经过长期的工艺探索,成功刻蚀出SiC多级沟槽结构,并开发出SiC多级沟槽JBS原型器件,实现了产品级技术的战略储备。如图3所示,该1200V/20A多级沟槽JBS器件与相同工艺制备的平面JBS器件相比,反向漏电流降低了2个数量级,击穿电压增加了约200V,同时正向导通电阻没有明显增加。多级沟槽JBS器件在常温下施加1200V反向电压时的反向漏电流低于60nA,在175℃及以上的高温环境下漏电流也仅为μA级别,非常适合应用于电动汽车或高温恶劣环境的工控系统的功率模块。

(图3 SiC多级沟槽JBS流片及电性测试结果:(a)多级沟槽JBS芯片的光学显微镜观测图;(b)芯片的SEM切片分析结果;多级沟槽JBS与传统JBS的(c)反向特性I-V曲线对比;(d)正向特性I-V曲线对比)

碳化硅沟槽MOSFET技术

SiC沟槽MOSFET在实际工艺制作和应用中仍然存在几个问题:1.SiC漂移区的高电场导致栅氧化层上的电场很高;2.实际开关过程中的电压浪涌由器件本身承受,引起器件可靠性问题;3.离子注入深度有限,导致很多设计从工艺上难以实现。业界目前仅有两种规模量产的SiC沟槽MOSFET专利结构,其中日本Rohm采用在栅极沟槽两侧构造源极双沟槽结构屏蔽中间的栅极沟槽底部,德国Infineon采用“P+半包裹的非对称沟槽结构”。国内对于沟槽MOSFET的研究才刚刚起步。九峰山实验室前瞻性地完成了专利布局,包括“胶囊沟槽”系列,“包角沟槽”系列,“双侧导通半包沟槽”系列等,并在进一步完善相关技术的专利布局。

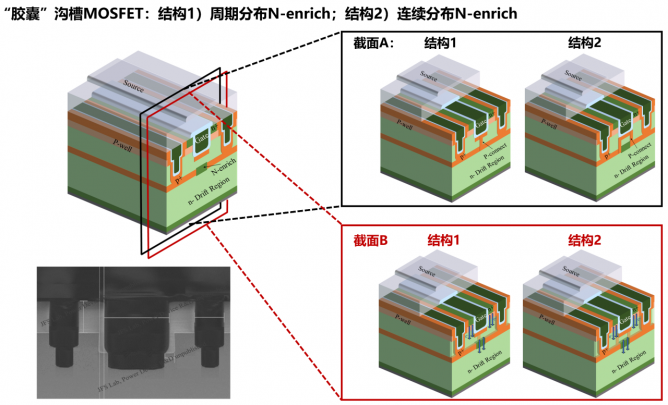

(图4 SiC“胶囊”沟槽MOSFET结构示意图)

如图4所示,为九峰山实验室的“胶囊沟槽”结构。该方案在栅极沟槽的两侧设计了P+掩蔽结构,并且通过二次外延的方法在n-漂移层中形成P+埋层来达到电场屏蔽的效果,同时在栅极沟槽底部设计p-shield来进一步保护沟槽底部及拐角位置的栅氧,p-shield通过周期性的与P+埋层连接来实现接地效果,通过向栅极沟槽下方的P+埋层注入n型离子形成N-Enrich区域的方式来形成导电通路。

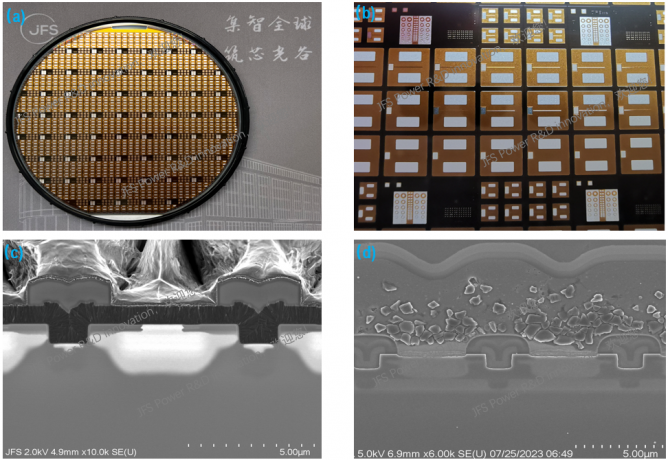

(图5 SiC“胶囊”沟槽MOSFET DEMO晶圆及器件SEM结构)

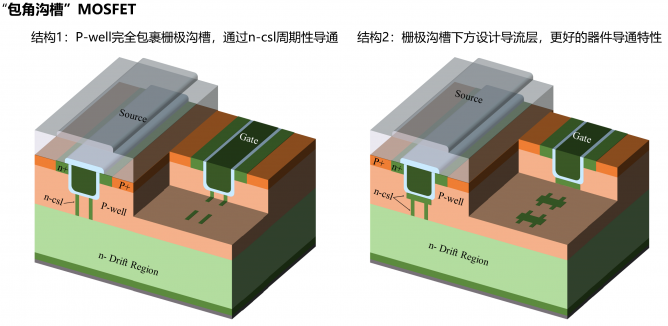

如图6所示,为九峰山实验室的“包角沟槽”结构。该方案通过构造比栅极沟槽更深的P阱区,使P阱区包住槽角,通过沟槽底部的两条柱状N型离子注入区形成导电通道。导电通道在沿沟槽方向是间断排布的,使得导电通道中间的P型区域可以通过与P阱区互联从而接地。当器件工作在反向阻断状态时,沟槽下方的N型导电通道区和P阱之间会相互耗尽、达到半超结效果,在提高器件击穿电压的同时也可以降低器件的导通电阻。P阱区可以通过二次外延形成,避免了对产能影响严重的SiC高温高能Al离子注入工艺,整体方案在提升SiC沟槽MOSFET性能的同时,还兼顾对fab厂制备产能的提升。

(图6 SiC“包角”沟槽MOSFET结构示意图)

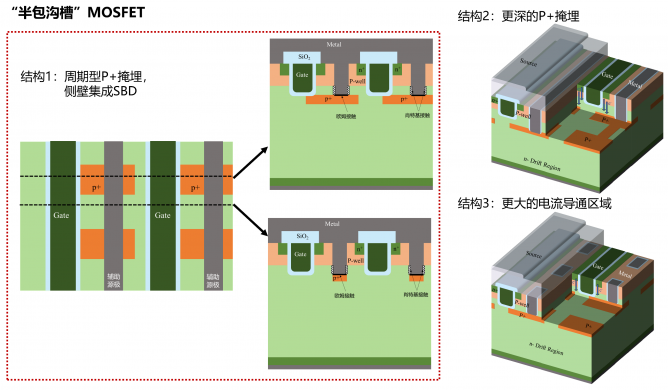

如图7所示,为九峰山实验室的“半包沟槽”结构。采用Infineon的“半包沟槽”结构会造成沟槽MOSFET只能通过一侧沟道来导电,另一侧被用来构造P+屏蔽层从而牺牲了导电沟道。九峰山实验室的双侧导通“半包沟槽”结构采用一侧构造辅助源极沟槽,使得栅极沟槽两侧的沟道都可以进行电子的输运,构造更好的双侧导通能力的“半包沟槽”MOSFET。P+掩埋层通过辅助源极沟槽接地,在空间上呈周期性分布,当栅极沟槽底部没有P+掩埋层时栅极两侧沟道都可以导通。同时,可以在辅助源极沟槽的侧壁集成肖特基二极管,底部形成欧姆接触,形成更好的续流特性。

(图7 SiC“半包”沟槽MOSFET结构示意图)